# CMS8S5880 User Manual

Enhanced Flash 8 bit 1T 8051- Microcontroller Rev. 1.3.7

#### Please note the following CMS IP policy

\*Zhongwei Semiconductor (Shenzhen) Co., Ltd. (hereinafter referred to as the Company) has applied for a patent and enjoys absolute legal rights and interests. The patent rights related to the Company's MCUs or other products have not been authorized to be licensed, and any company, organization or individual who infringes the Company's patent rights through improper means will take all possible legal actions to curb the infringer's improper infringement and recover the losses suffered by the Company as a result of the infringement or the illegal benefits obtained by the infringer.

\*The name and logo of Zhongwei Semiconductor (Shenzhen) Co., Ltd. are registered trademarks of the Company.

\*The Company reserves the right to further explain the reliability, functionality and design improvements of the products in the data sheet. However, the Company is not responsible for the use of the Specification Contents. The applications mentioned herein are for illustrative purposes only and the Company does not warrant and does not represent that these applications can be applied without further modification, nor does it recommend that its products be used in places that may cause harm to persons due to malfunction or other reasons. The Company's products are not licensed for lifesaving, life-sustaining devices or systems as critical devices. The Company reserves the right to modify the product without prior notice, please refer to the official website www.mcu.com.cn for the latest information.

# **Contents**

| 1. PF | RODUCT DESCRIPTION                         | 9  |

|-------|--------------------------------------------|----|

| 1.1   | Functional Characteristics                 | 9  |

| 1.2   | System Block Diagram                       | 10 |

| 1.3   | Pin Distribution                           | 11 |

| 1.3   | 3.1 CMS8S5880-TSSOP20 Pin map              | 11 |

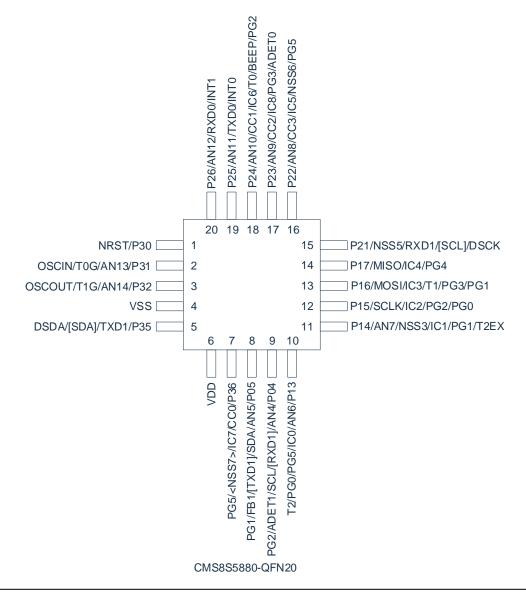

| 1.3   | 3.2 CMS8S5880-QFN20 Pin map                | 11 |

| 1.4   | System Configuration Register              | 15 |

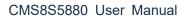

| 1.5   | Online Serial Programming                  | 16 |

| 2. CI | ENTRAL PROCESSING UNIT (CPU)               | 17 |

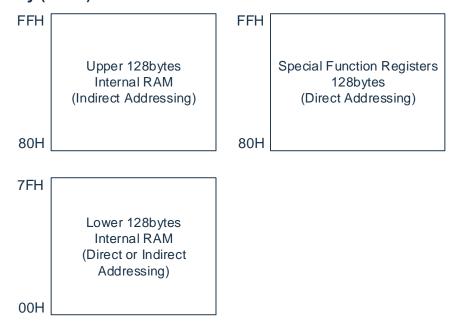

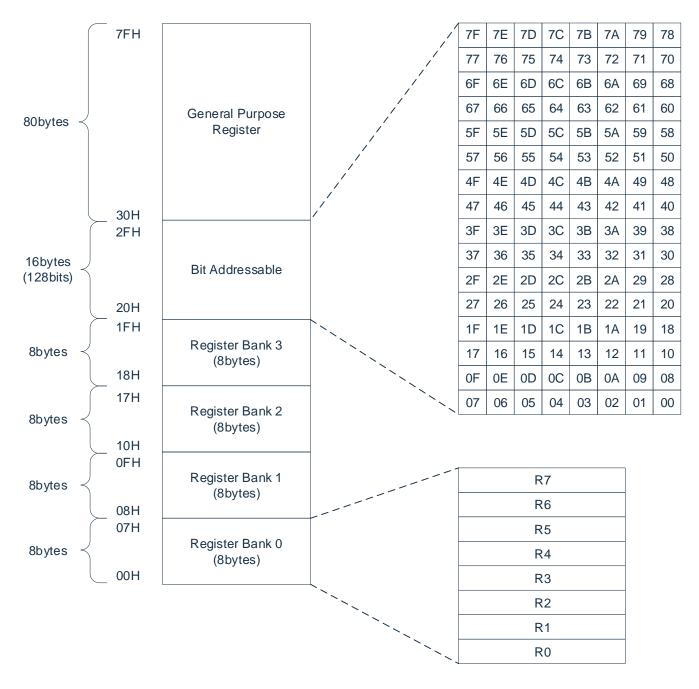

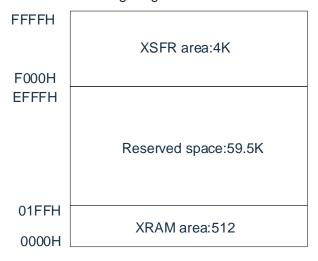

| 2.1   | Memory                                     | 17 |

| 2.1   | 1.1 Program Memory                         | 17 |

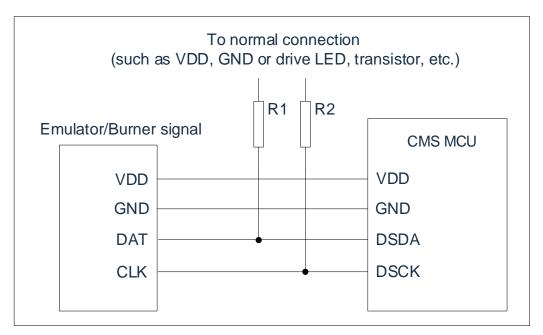

| 2.1   | 1.2 Reset Vector (0000H)                   | 17 |

| 2.1   | 1.3 Data Memory (IRAM)                     | 18 |

| 2.1   | 1.4 Special Function Register Table (SFR)  | 20 |

| 2.1   | 1.5 External Data Memory (XRAM)            | 21 |

| 2.1   | 1.6 Special Function Register Table (XSFR) | 22 |

| 2.2   | Accumulator (ACC)                          | 26 |

| 2.3   | B Register (B)                             | 26 |

| 2.4   | Stack Pointer Register (SP)                | 26 |

| 2.5   | Data Pointer Register (DPTR0/DPTR1)        | 26 |

| 2.6   | Data Pointer Selection Register (DPS)      | 26 |

| 2.7   | Program Status Register (PSW)              | 27 |

| 2.8   | Program Counter (PC)                       | 28 |

| 2.9   | Timing Access Register (TA)                | 28 |

| 2.10  | Watch Dog TIMER (WDT)                      | 29 |

| 2.1   | 10.1 WDT Overflow Period                   | 29 |

| 2.1   | 10.2 Watch Dog Control Register WDCON      | 29 |

| 2.1   | 10.3 WDT Overflow Control Register CKCON   | 30 |

| 2.11  | Function Control Register (FUNCCR)         | 31 |

| 3. S  | YSTEM CLOCK                                | 32 |

| 3.1   | System Oscillators                         | 32 |

| 3.2   | Reset Time                                 | 32 |

| 3.3   | Clock Structure                            | 33 |

| 3.3   | 3.1 Clock Control Register                 | 33 |

| 3.3   | 3.2 Oscillator Control Register CLKDIV     | 33 |

| 3.3   | 3.3 Function Clock Control Register CKCON  | 33 |

| 4. RI | ESET                                       | 34 |

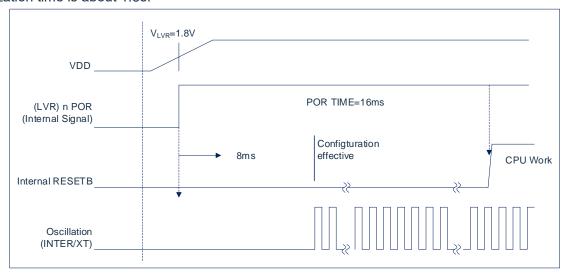

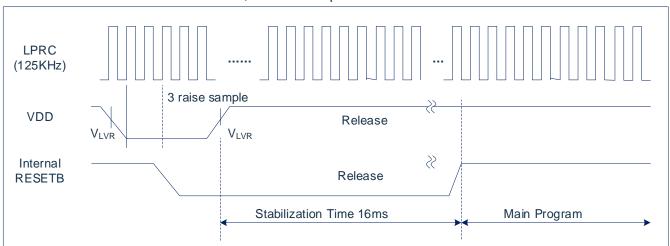

| 4.1   | Power-on Reset                             | 34 |

| 4.2   | External Reset                             | 36 |

| 4.3   | Low Voltage Reset                          | 36 |

| 4.4   | Watchdog Reset (WDT)                       |    |

|       |                                            |    |

|    | 4.5   | Software Reset                                 | 38 |

|----|-------|------------------------------------------------|----|

|    | 4.6   | CONFIG Status Protection Reset                 | 38 |

|    | 4.7   | Power-on Configuration Monitoring Reset        | 38 |

| 5. | POV   | WER MANAGEMENT                                 | 39 |

|    | 5.1   | Power Management Register PCON                 | 39 |

|    | 5.2   | Idle Mode                                      | 39 |

|    | 5.3   | Sleep Mode                                     | 40 |

|    | 5.3.1 | Wake From Sleep Mode                           | 40 |

|    | 5.3.2 | Wake Waiting Status                            | 40 |

|    | 5.3.3 | Wake Up Time in Sleep Mode                     | 41 |

|    | 5.3.4 | Reset To Reboot The System                     | 41 |

|    | 5.4   | Sleep Mode Application Example                 | 42 |

|    | 5.5   | Sleep Power Consumption In Debug Mode          | 42 |

| 6. | I/O F | PORT                                           | 43 |

|    | 6.1   | GPIO Function                                  | 43 |

|    | 6.1.1 | PORTx Data Register Px                         | 43 |

|    | 6.1.2 | PORTx Direction Register PxTRIS                | 43 |

|    | 6.1.3 | PORTx Open-Drain Control Register PxOD         | 44 |

|    | 6.1.4 | PORTx Pull-up Resistor Control Register PxUP   | 44 |

|    | 6.1.5 | PORTx Pull-Down Resistor Control Register PxRD | 44 |

|    | 6.2   | Multiplexing Functions                         | 45 |

|    | 6.2.1 | Port Configuration Registers                   | 45 |

|    | 6.2.2 | Port External Interrupt Control Register       | 46 |

| 7. | INTE  | ERRUPT                                         | 47 |

|    | 7.1   | Overview                                       | 47 |

|    | 7.2   | External Interrupt                             | 48 |

|    | 7.2.1 | INT0/INT1 Interrupt                            | 48 |

|    | 7.2.2 | GPIO Interrupt                                 | 48 |

|    | 7.2.3 | Interrupt and Wake Up from Sleep               | 48 |

|    | 7.3   | Interrupt Register                             | 49 |

|    | 7.3.1 | Interrupt Mask Register                        | 49 |

|    | 7.3.2 | Interrupt Priority Control Register            | 53 |

|    | 7.3.3 | Interrupt Flag Bit Register                    | 55 |

|    | 7.3.4 | Clearance of Interrupt Flag Bit                | 62 |

|    | 7.3.5 | Special Interrupt Flag Bits In Debug Mode      | 63 |

| 8. | TIMI  | ING COUNTER 0/1 (TIMER0/1)                     | 64 |

|    | 8.1   | Overview                                       | 64 |

|    | 8.2   | Timer 0/1 Register                             | 65 |

|    | 8.2.1 | Timer 0/1 mode register TMOD                   | 65 |

|    | 8.2.2 | Timer0/1 Control Register TCON (Addressable)   | 66 |

|    | 8.2.3 | Timer 0 Data Register Lower Bit TL0            | 66 |

|    | 8.2.4 | Timer 0 Data Register Higher Bit TH0           | 67 |

|    | 8.2.5  | Timer 1 Data Register Lower Bit TL1                      | 67 |

|----|--------|----------------------------------------------------------|----|

|    | 8.2.6  | Timer 1 Data Register Higher Bit TH1                     | 67 |

|    | 8.2.7  | Function Clock Control Register CKCON                    | 67 |

|    | 8.3 T  | Fimer 0/1 Interrupt                                      | 68 |

|    | 8.4 T  | Fimer 0 Operating Mode                                   | 71 |

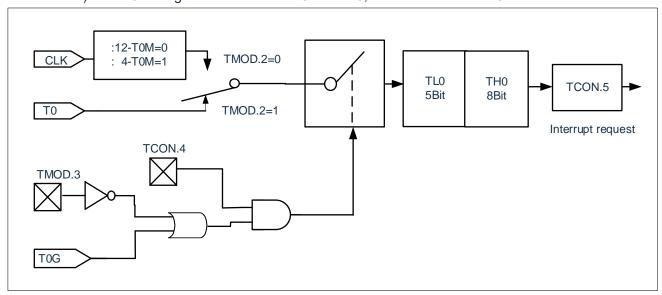

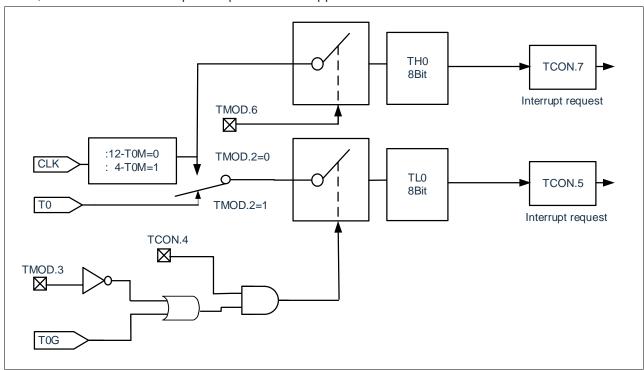

|    | 8.4.1  | T0 - Mode 0 (13-Bit Timing/Counting Mode)                | 71 |

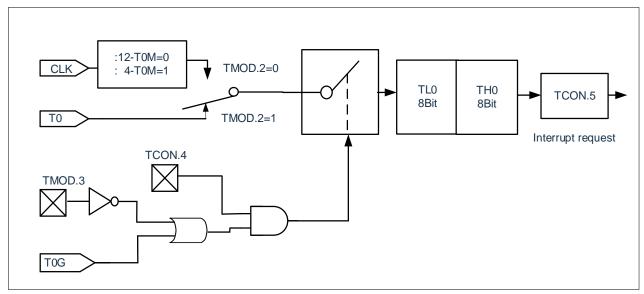

|    | 8.4.2  | T0 -Mode 1 (16-bit timer/count mode)                     | 71 |

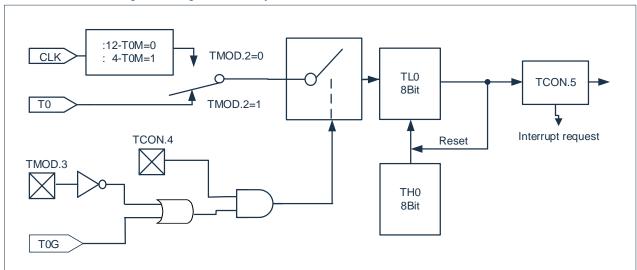

|    | 8.4.3  | T0 - Mode 2 (8-bit auto reload timing / counting mode)   | 72 |

|    | 8.4.4  | T0 - Mode3 (Two separate 8-bit timer/counters)           | 73 |

|    | 8.5 T  | Timer 1 Operation Mode                                   | 74 |

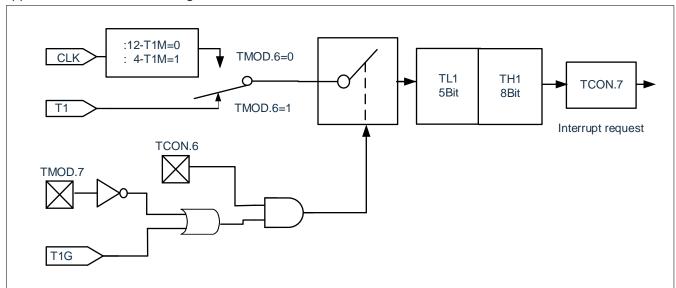

|    | 8.5.1  | T1 -Mode0 (13-bit Timer/Count Mode)                      | 74 |

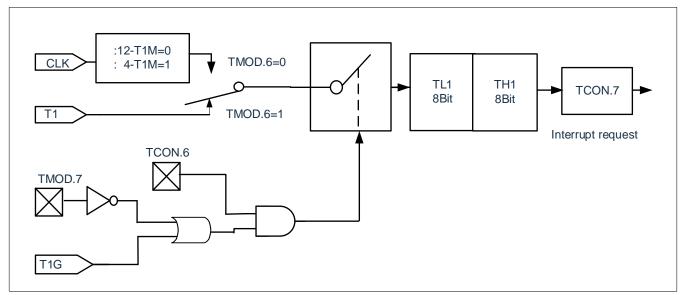

|    | 8.5.2  | T1 - Mode1 (16-bit Timer/Count Mode)                     | 74 |

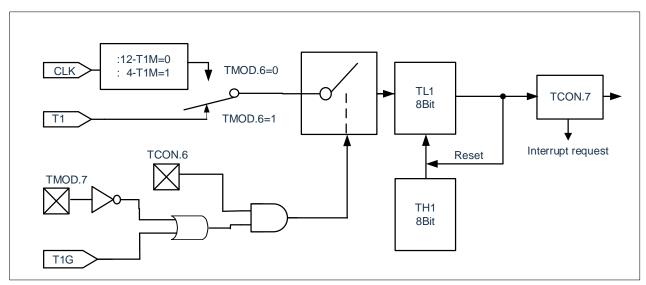

|    | 8.5.3  | T1 -Mode2 (8-bit Auto Reload Timing/Counting Mode)       | 75 |

|    | 8.5.4  | T1 - Mode3 (Stop Counting)                               | 75 |

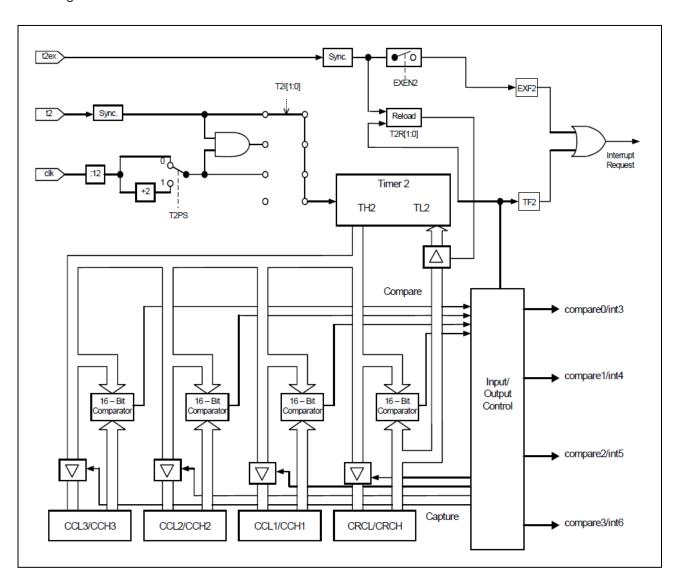

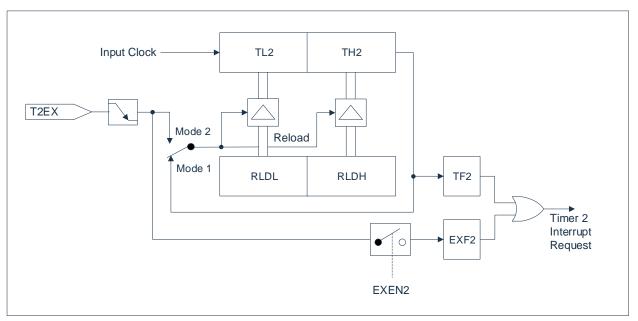

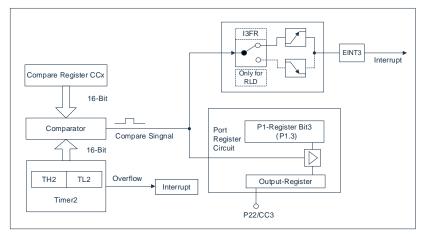

| 9. | TIMII  | NG COUNTER 2 (TIMER2)                                    | 76 |

|    | 9.1 C  | Overview                                                 | 76 |

|    | 9.2 T  | Fimer2 Register                                          | 77 |

|    | 9.2.1  | T2CON                                                    | 77 |

|    | 9.2.2  | Timer2 Data Register Lower Bit TL2                       | 78 |

|    | 9.2.3  | Timer2 Data Register Higher Bit TH2                      | 78 |

|    | 9.2.4  | Timer2 compare/capture/reload register low 8-bit RLDL    | 78 |

|    | 9.2.5  | Timer2 compare/capture/reload register high 8-bit RLDH   | 78 |

|    | 9.2.6  | Timer2 compare/capture channel1 register low 8-bit CCL1  | 78 |

|    | 9.2.7  | Timer2 compare/capture channel1 register high 8-bit CCH1 | 79 |

|    | 9.2.8  | Timer2 compare/capture channel2 register low 8-bit CCL2  | 79 |

|    | 9.2.9  | Timer2 compare/capture channel2 register high 8-bit CCH2 | 79 |

|    | 9.2.10 | Timer2 compare/capture channel3 register low 8-bit CCL3  | 79 |

|    | 9.2.11 | Timer2 compare/capture channel3 register high 8-bit CCH3 | 79 |

|    | 9.2.12 | Timer2 compare/capture control register CCEN             | 80 |

|    | 9.2.13 | Timer2 capture channel input choose register0 CAPCR0     | 81 |

|    | 9.2.14 | Timer2 capture channel input choose register1 CAPCR1     | 81 |

|    | 9.3 T  | Timer2 Interrupt                                         | 82 |

|    | 9.3.1  | Timer Interrupt                                          | 86 |

|    | 9.3.2  | External Trigger Interrupt                               | 86 |

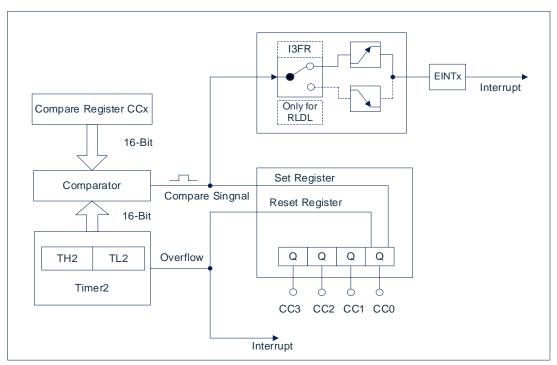

|    | 9.3.3  | Compare Interrupt                                        | 86 |

|    | 9.3.4  | Capture interrupt                                        | 86 |

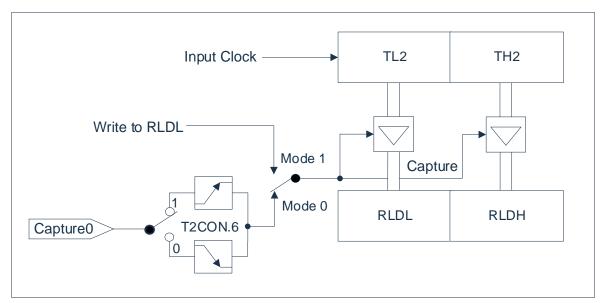

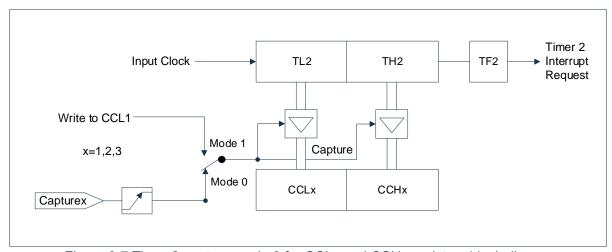

|    | 9.4 T  | Timer2 Function Description                              | 87 |

|    | 9.4.1  | T2 Timing Mode                                           |    |

|    | 9.4.2  | T2 Reload Mode                                           |    |

|    | 9.4.3  | Timer2 Gated Timing Mode                                 |    |

|    | 9.4.4  | Timer2 Event Counting Mode                               |    |

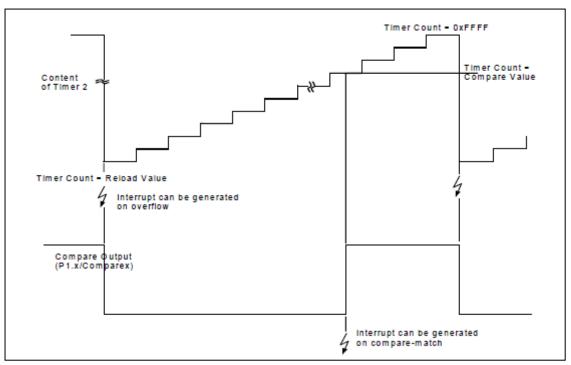

|    | 9.5 C  | Compare/PWM function                                     |    |

|    | 9.5.1  | Compare Mode 0                                           | 89 |

| 9.6.1 Capture Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9.5.2    | Compare Mode 1                                    | 90  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------|-----|

| 9.6.2 Capture Mode 1       .92         0. TIMER 3/4       .93         10.1 Overview       .93         10.2 Timer 3/4 Register       .94         10.2.1 Timer 3/4 Control Register T34MOD       .94         10.2.2 Timer 3 Data Register Lower Bit TL3       .94         10.2.3 Timer 3 Data Register Higher Bit TH3       .95         10.2.4 Timer 4 Data Register Lower Bit TL4       .95         10.2.5 Timer 4 Data Register Higher Bit TH4       .95         10.3 Timer 3/4 Interrupt       .96         10.4 Timer3 Operation Mode       .98         10.4.1 Til 3 - Mode0 (13-bit Timing Mode)       .98         10.4.2 Til 3 - Mode1 (16 - bit timing mode)       .98         10.4.3 Til 3 - Mode2 (8-bit automatic reload timing mode)       .99         10.4 Til 4 - Mode0 (13 - bit Timing Mode)       .99         10.5 Timer4 Operation Mode       .100         10.5.1 Til 4 - Mode0 (16 - bit Timing mode)       .100         10.5.2 Til 4 - Mode0 (16 - bit Timing mode)       .100         10.5.1 Timer4 Operation Mode       .100         10.5.2 Til 4 - Mode0 (16 - bit Timing Mode)       .100         10.5.3 Til 4 - Mode0 (16 - bit Timing Mode)       .100         10.5.4 Til 4 - Mode0 (16 - bit Timing Mode)       .100         10.5.2 Til 4 - Mode0 (16 - bit Timing Mod                                           | 9.6      | Capture Function                                  | 91  |

| 0. TIMER 3/4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9.6.1    | Capture Mode 0                                    | 91  |

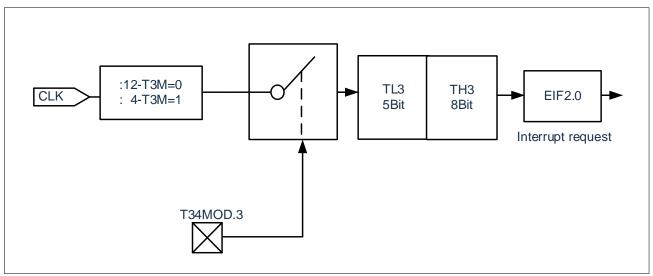

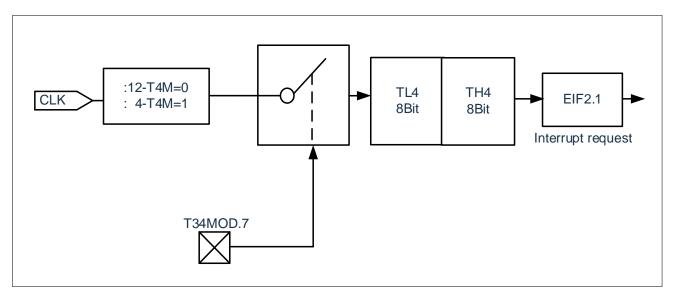

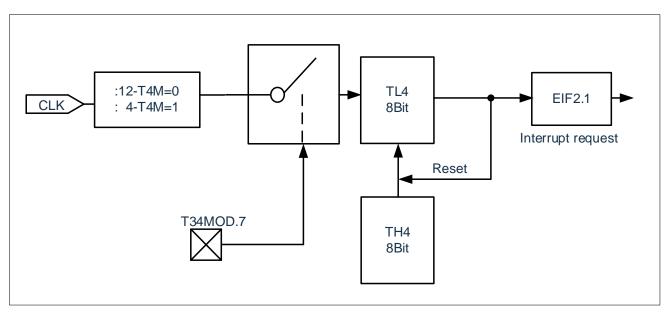

| 10.1       Overview       93         10.2       Timer 3/4 Register       94         10.2.1       Timer 3/4 Control Register T34MOD       94         10.2.2       Timer 3 Data Register Lower Bit TL3       94         10.2.3       Timer 3 Data Register Lower Bit TH3       95         10.2.4       Timer 4 Data Register Higher Bit TH4       95         10.2.5       Timer 3/4 Interrupt       96         10.4       Timer 3 Operation Mode       98         10.4.1       T3 - Mode0 (13-bit Timing Mode)       98         10.4.2       T3 - Mode1 (16 -bit timing mode)       98         10.4.3       T3 - Mode2 (8-bit automatic reload timing mode)       99         10.5       Timer4 Operation Mode       100         10.5.1       T4 - Mode0 (13 -bit timing mode)       100         10.5.2       T4 - Mode1 (16 -bit Timing Mode)       100         10.5.2       T4 - Mode3 (stop counting)       101         10.5.4       T4 - Mode3 (stop counting)       101         12.1       ADC Overview       103                                                                                                                                       | 9.6.2    | Capture Mode 1                                    | 92  |

| 10.2 Timer 3/4 Register       .94         10.2.1 Timer 3/4 Control Register T34MOD       .94         10.2.2 Timer 3 Data Register Lower Bit TL3       .94         10.2.3 Timer 3 Data Register Higher Bit TH3       .95         10.2.4 Timer 4 Data Register Higher Bit TH4       .95         10.2.5 Timer 4 Data Register Higher Bit TH4       .95         10.3 Timer 3/4 Interrupt       .96         10.4 Timer3 Operation Mode       .98         10.4.1 T3 - Mode0 (13-bit Timing Mode)       .98         10.4.2 T3 - Mode1 (16 - bit timing mode)       .98         10.4.3 T3 - Mode2 (8-bit automatic reload timing mode)       .99         10.4 T3 - Mode3 (Two separate 8-bit timers)       .99         10.5 Timer4 Operation Mode       .10         10.5.1 T4 - Mode0 (13 - bit timing mode)       .10         10.5.2 T4 - Mode1 (16 - bit Timing Mode)       .10         10.5.3 T4 - Mode2 (8-bit automatic reload timing mode)       .10         10.5.4 T4 - Mode3 (stop counting)       .10         10.5.2 T4 - Mode3 (stop counting)       .10         10.5.4 T4 - Mode3 (stop counting)       .10         10.5.2 T4 - Mode3 (stop counting)       .10         10.5.4 T4 - Mode3 (stop counting)       .10         12.1 ADC Overview       .10         12.2 ADC Configuration <th>10. TIMI</th> <th>ER 3/4</th> <th>93</th> | 10. TIMI | ER 3/4                                            | 93  |

| 10.2.1 Timer 3/4 Control Register T34MOD. 94 10.2.2 Timer 3 Data Register Lower Bit TL3. 94 10.2.3 Timer 3 Data Register Lower Bit TH3. 95 10.2.4 Timer 4 Data Register Lower Bit TH4. 95 10.2.5 Timer 4 Data Register Higher Bit TH4. 95 10.3 Timer 3/4 Interrupt. 96 10.4 Timer3 Operation Mode. 98 10.4.1 T3 - Mode0 (13-bit Timing Mode). 98 10.4.2 T3 - Mode1 (16 -bit timing mode). 98 10.4.3 T3 - Mode2 (8-bit automatic reload timing mode). 99 10.5.4 T3 - Mode0 (13 -bit timing mode). 99 10.5.1 T4 - Mode0 (13 -bit timing mode). 100 10.5.1 T4 - Mode0 (13 -bit timing mode). 100 10.5.2 T4 - Mode1 (16 -bit Timing Mode). 100 10.5.3 T4- Mode3 (8-bit automatic reload timing mode). 101 10.5.4 T4 - Mode3 (8-bit automatic reload timing mode). 101 10.5.4 TA - Mode3 (stop counting). 101 11. BUZZER 102 2. ANALOG TO DIGITAL CONVERSION (ADC) 103 12.1 ADC Overview. 103 12.2 ADC Configuration 104 12.2.1 Port Configuration 104 12.2.2 Channel Selection 104 12.2.3 ADC Reference Voltage 104 12.2.4 Conversion Clock 104 12.2.5 ADC Interrupt 105 12.2.6 Result Formatting 105 12.3.1 External Port Edge Triggered ADC 106                                                                                                                                                                                           | 10.1     | Overview                                          | 93  |

| 10.2.2 Timer 3 Data Register Lower Bit TL3       94         10.2.3 Timer 3 Data Register Higher Bit TH3       95         10.2.4 Timer 4 Data Register Lower Bit TL4       95         10.2.5 Timer 4 Data Register Higher Bit TH4       95         10.3 Timer 3/4 Interrupt       96         10.4 Timer3 Operation Mode       98         10.4.1 T3 - Mode0 (13-bit Timing Mode)       98         10.4.2 T3 - Mode1 (16 –bit timing mode)       98         10.4.3 T3 - Mode2 (8-bit automatic reload timing mode)       99         10.4 T3 - Mode3 (Two separate 8-bit timers)       99         10.5 Timer4 Operation Mode       100         10.5.1 T4 - Mode0 (13 –bit timing mode)       100         10.5.2 T4 —Mode1 (16 –bit Timing Mode)       100         10.5.3 T4- Mode2 (8-bit automatic reload timing mode)       101         10.5.4 T4- Mode3 (stop counting)       101         10.5.4 TA- Mode3 (stop counting)       101         1.5.2 ANALOG TO DIGITAL CONVERSION (ADC)       103         12.1 ADC Overview       103         12.2 ADC Configuration       104         12.2.1 Port Configuration       104         12.2.2 Channel Selection       104         12.2.3 ADC Reference Voltage       104         12.2.6 Result Formatting       105                                                                            | 10.2     | Timer 3/4 Register                                | 94  |

| 10.2.3 Timer 3 Data Register Higher Bit TH3       .95         10.2.4 Timer 4 Data Register Lower Bit TL4       .95         10.2.5 Timer 4 Data Register Higher Bit TH4       .95         10.3 Timer 3/4 Interrupt       .96         10.4 Timer3 Operation Mode       .98         10.4.1 T3 - Mode0 (13-bit Timing Mode)       .98         10.4.2 T3 - Mode1 (16 -bit timing mode)       .98         10.4.3 T3 - Mode2 (8-bit automatic reload timing mode)       .99         10.5 Timer4 Operation Mode       .100         10.5.1 T4 - Mode0 (13 - bit timing mode)       .100         10.5.2 T4 - Mode1 (16 - bit Timing Mode)       .100         10.5.3 T4- Mode2 (8-bit automatic reload timing mode)       .100         10.5.4 T4- Mode3 (stop counting)       .101         10.5.4 T4- Mode3 (stop counting)       .101         1. BUZZER       .102         2. ANALOG TO DIGITAL CONVERSION (ADC)       .103         12.1 ADC Overview       .103         12.2 ADC Configuration       .104         12.2.1 Port Configuration       .104         12.2.2 Channel Selection       .104         12.2.3 ADC Reference Voltage       .104         12.2.4 Conversion Clock       .104         12.2.5 ADC Interrupt       .105         12.2.6 Result Formatt                                                                              | 10.2.1   | 1 Timer 3/4 Control Register T34MOD               | 94  |

| 10.2.4 Timer 4 Data Register Lower Bit TL4       .95         10.2.5 Timer 4 Data Register Higher Bit TH4       .95         10.3 Timer 3/4 Interrupt       .96         10.4 Timer3 Operation Mode       .98         10.4.1 T3 - Mode0 (13-bit Timing Mode)       .98         10.4.2 T3 - Mode1 (16 - bit timing mode)       .98         10.4.3 T3 - Mode2 (8-bit automatic reload timing mode)       .99         10.5 Timer4 Operation Mode       .100         10.5.1 T4 - Mode0 (13 - bit timing mode)       .100         10.5.2 T4 - Mode1 (16 - bit Timing Mode)       .100         10.5.3 T4 - Mode2 (8-bit automatic reload timing mode)       .100         10.5.1 T4 - Mode2 (8-bit automatic reload timing mode)       .101         10.5.2 T4 - Mode3 (stop counting)       .101         1.5.4 T4 - Mode3 (stop counting)       .101         1.5.4 T4 - Mode3 (stop counting)       .101         1. BUZZER       .102         2. ANALOG TO DIGITAL CONVERSION (ADC)       .103         12.1 ADC Overview       .103         12.2 ADC Configuration       .104         12.2.1 Port Configuration       .104         12.2.2 Channel Selection       .104         12.2.3 ADC Reference Voltage       .104         12.2.4 Conversion Clock       .104                                                                                 | 10.2.2   | 2 Timer 3 Data Register Lower Bit TL3             | 94  |

| 10.2.5 Timer 4 Data Register Higher Bit TH4       .95         10.3 Timer 3/4 Interrupt       .96         10.4 Timer3 Operation Mode       .98         10.4.1 T3 - Mode0 (13-bit Timing Mode)       .98         10.4.2 T3 - Mode1 (16 – bit timing mode)       .98         10.4.3 T3 - Mode2 (8-bit automatic reload timing mode)       .99         10.4.4 T3 - Mode3 (Two separate 8-bit timers)       .99         10.5 Timer4 Operation Mode       .100         10.5.1 T4 - Mode0 (13 – bit timing mode)       .100         10.5.2 T4 - Mode1 (16 – bit Timing Mode)       .100         10.5.3 T4- Mode2 (8-bit automatic reload timing mode)       .101         10.5.4 T4- Mode3 (stop counting)       .101         1. BUZZER       .102         2. ANALOG TO DIGITAL CONVERSION (ADC)       .103         12.1 ADC Overview       .103         12.2 ADC Configuration       .104         12.2.1 Port Configuration       .104         12.2.2 Channel Selection       .104         12.2.3 ADC Reference Voltage       .104         12.2.5 ADC Interrupt       .105         12.2.6 Result Formatting       .105         12.3 ADC Hardware Triggered Start       .106         12.3.1 External Port Edge Trigger ADC       .106         12.3.2 PWM Triggered                                                                              | 10.2.3   | 3 Timer 3 Data Register Higher Bit TH3            | 95  |

| 10.3       Timer 3/4 Interrupt       96         10.4       Timer3 Operation Mode       98         10.4.1       T3 - Mode0 (13-bit Timing Mode)       98         10.4.2       T3 - Mode1 (16 - bit timing mode)       98         10.4.3       T3 - Mode2 (8-bit automatic reload timing mode)       99         10.4.4       T3 - Mode3 (Two separate 8-bit timers)       99         10.5       Timer4 Operation Mode       100         10.5.1       T4 - Mode0 (13 - bit timing mode)       100         10.5.2       T4 - Mode1 (16 - bit Timing Mode)       100         10.5.3       T4- Mode2 (8-bit automatic reload timing mode)       101         10.5.4       T4- Mode3 (stop counting)       101         1.5.4       T4- Mode3 (stop counting)       101         1.5.4       TA- Mode3 (stop counting)       101         1.5.4       TA- Mode3 (stop counting)       101         1.5.4       TA- Mode3 (stop counting)       101         1.5.2       ADC ODIGITAL CONVERSION (ADC)       103         12.1       ADC Overview       103         12.2.1       Port Configuration       104         12.2.2       Channel Selection       104         12.2.3       ADC Reference Voltage       104                                                                                                                                    | 10.2.4   | 4 Timer 4 Data Register Lower Bit TL4             | 95  |

| 10.4       Timer3 Operation Mode       98         10.4.1       T3 - Mode0 (13-bit Timing Mode)       98         10.4.2       T3 - Mode1 (16 - bit timing mode)       98         10.4.3       T3 - Mode2 (8-bit automatic reload timing mode)       99         10.4       T3 - Mode3 (Two separate 8-bit timers)       99         10.5       Timer4 Operation Mode       100         10.5.1       T4 - Mode0 (13 - bit timing mode)       100         10.5.2       T4 - Mode1 (16 - bit Timing Mode)       100         10.5.3       T4- Mode2 (8-bit automatic reload timing mode)       101         10.5.4       T4- Mode3 (stop counting)       101         1.       BUZZER       102         2.       ANALOG TO DIGITAL CONVERSION (ADC)       103         12.1       ADC Overview       103         12.2       ADC Configuration       104         12.2.1       Port Configuration       104         12.2.2       Channel Selection       104         12.2.3       ADC Reference Voltage       104         12.2.4       Conversion Clock       104         12.2.5       ADC Interrupt       105         12.2.6       Result Formatting       105         12.3.1       <                                                                                                                                                              | 10.2.5   | 5 Timer 4 Data Register Higher Bit TH4            | 95  |

| 10.4.1 T3 - Mode0 (13-bit Timing Mode).       98         10.4.2 T3 - Mode1 (16 - bit timing mode).       98         10.4.3 T3 - Mode2 (8-bit automatic reload timing mode).       99         10.4 T3 - Mode3 (Two separate 8-bit timers).       99         10.5 Timer4 Operation Mode.       100         10.5.1 T4 - Mode0 (13 - bit timing mode).       100         10.5.2 T4 - Mode1 (16 - bit Timing Mode)       100         10.5.3 T4- Mode2 (8-bit automatic reload timing mode).       101         10.5.4 T4- Mode3 (stop counting).       101         1. BUZZER.       102         2. ANALOG TO DIGITAL CONVERSION (ADC)       103         12.1 ADC Overview.       103         12.2 ADC Configuration.       104         12.2.1 Port Configuration.       104         12.2.2 Channel Selection.       104         12.2.3 ADC Reference Voltage.       104         12.2.4 Conversion Clock.       104         12.2.5 ADC Interrupt.       105         12.2.6 Result Formatting.       105         12.3 ADC Hardware Triggered Start.       106         12.3.1 External Port Edge Trigger ADC.       106         12.3.2 PWM Triggered ADC.       106                                                                                                                                                                              | 10.3     | Timer 3/4 Interrupt                               | 96  |

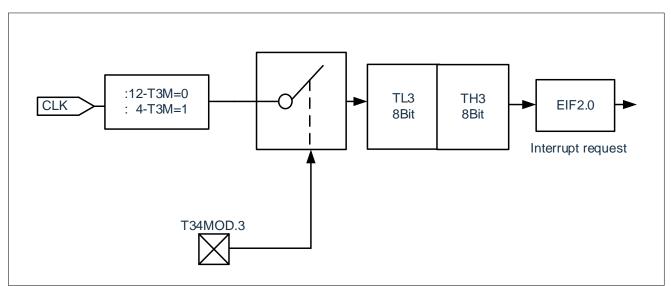

| 10.4.2 T3 - Mode1 (16 -bit timing mode)       98         10.4.3 T3 - Mode2 (8-bit automatic reload timing mode)       99         10.4.4 T3 - Mode3 (Two separate 8-bit timers)       99         10.5 Timer4 Operation Mode       100         10.5.1 T4 - Mode0 (13 - bit timing mode)       100         10.5.2 T4 - Mode1 (16 - bit Timing Mode)       100         10.5.3 T4- Mode2 (8-bit automatic reload timing mode)       101         10.5.4 T4- Mode3 (stop counting)       101         1. BUZZER       102         2. ANALOG TO DIGITAL CONVERSION (ADC)       103         12.1 ADC Overview       103         12.2 ADC Configuration       104         12.2.1 Port Configuration       104         12.2.2 Channel Selection       104         12.2.3 ADC Reference Voltage       104         12.2.4 Conversion Clock       104         12.2.5 ADC Interrupt       105         12.2.6 Result Formatting       105         12.3 ADC Hardware Triggered Start       106         12.3.1 External Port Edge Trigger ADC       106         12.3.2 PWM Triggered ADC       106          12.3.2 PWM Triggered ADC       106                                                                                                                                                                                                             | 10.4     | Timer3 Operation Mode                             | 98  |

| 10.4.3 T3 - Mode2 (8-bit automatic reload timing mode).       .99         10.4.4 T3 -Mode3 (Two separate 8-bit timers).       .99         10.5 Timer4 Operation Mode.       .100         10.5.1 T4 -Mode0 (13 -bit timing mode).       .100         10.5.2 T4 -Mode1 (16 -bit Timing Mode).       .100         10.5.3 T4- Mode2 (8-bit automatic reload timing mode).       .101         10.5.4 T4- Mode3 (stop counting).       .101         1 BUZZER.       .102         2 ANALOG TO DIGITAL CONVERSION (ADC)       .103         12.1 ADC Overview.       .103         12.2 ADC Configuration.       .104         12.2.1 Port Configuration.       .104         12.2.2 Channel Selection.       .104         12.2.3 ADC Reference Voltage.       .104         12.2.4 Conversion Clock.       .104         12.2.5 ADC Interrupt.       .105         12.2.6 Result Formatting.       .105         12.3 ADC Hardware Triggered Start.       .106         12.3.1 External Port Edge Trigger ADC.       .106         12.3.2 PWM Triggered ADC.       .106                                                                                                                                                                                                                                                                                  | 10.4.1   | 1 T3 - Mode0 (13-bit Timing Mode)                 | 98  |

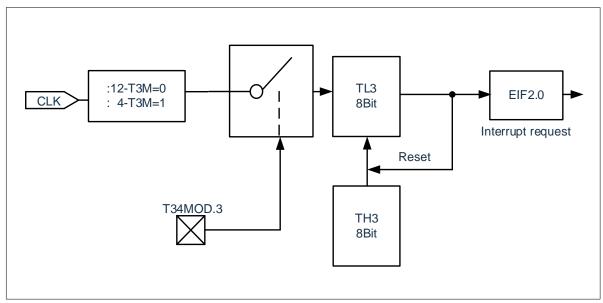

| 10.4.4 T3 -Mode3 (Two separate 8-bit timers)       .99         10.5 Timer4 Operation Mode       .100         10.5.1 T4 -Mode0 (13 -bit timing mode)       .100         10.5.2 T4 -Mode1 (16 -bit Timing Mode)       .100         10.5.3 T4- Mode2 (8-bit automatic reload timing mode)       .101         10.5.4 T4- Mode3 (stop counting)       .101         1. BUZZER       .102         2. ANALOG TO DIGITAL CONVERSION (ADC)       .103         12.1 ADC Overview       .103         12.2 ADC Configuration       .104         12.2.1 Port Configuration       .104         12.2.2 Channel Selection       .104         12.2.3 ADC Reference Voltage       .104         12.2.4 Conversion Clock       .104         12.2.5 ADC Interrupt       .105         12.2.6 Result Formatting       .105         12.3 ADC Hardware Triggered Start       .106         12.3.1 External Port Edge Trigger ADC       .106         12.3.2 PWM Triggered ADC       .106                                                                                                                                                                                                                                                                                                                                                                            | 10.4.2   | 2 T3 - Mode1 (16 -bit timing mode)                | 98  |

| 10.5       Timer4 Operation Mode.       100         10.5.1       T4 -Mode0 (13 -bit timing mode).       100         10.5.2       T4 -Mode1 (16 -bit Timing Mode)       100         10.5.3       T4- Mode2 (8-bit automatic reload timing mode).       101         10.5.4       T4- Mode3 (stop counting).       101         1       BUZZER       102         2.       ANALOG TO DIGITAL CONVERSION (ADC)       103         12.1       ADC Overview.       103         12.2       ADC Configuration       104         12.2.1       Port Configuration       104         12.2.2       Channel Selection       104         12.2.3       ADC Reference Voltage       104         12.2.4       Conversion Clock       104         12.2.5       ADC Interrupt       105         12.2.6       Result Formatting       105         12.3       ADC Hardware Triggered Start       106         12.3.1       External Port Edge Trigger ADC       106         12.3.2       PWM Triggered ADC       106                                                                                                                                                                                                                                                                                                                                             | 10.4.3   | 3 T3 - Mode2 (8-bit automatic reload timing mode) | 99  |

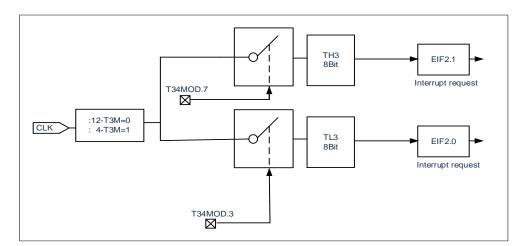

| 10.5.1 T4 - Mode0 (13 - bit timing mode)       100         10.5.2 T4 - Mode1 (16 - bit Timing Mode)       100         10.5.3 T4- Mode2 (8-bit automatic reload timing mode)       101         10.5.4 T4- Mode3 (stop counting)       101         1. BUZZER       102         2. ANALOG TO DIGITAL CONVERSION (ADC)       103         12.1 ADC Overview       103         12.2 ADC Configuration       104         12.2.1 Port Configuration       104         12.2.2 Channel Selection       104         12.2.3 ADC Reference Voltage       104         12.2.4 Conversion Clock       104         12.2.5 ADC Interrupt       105         12.2.6 Result Formatting       105         12.3 ADC Hardware Triggered Start       106         12.3.1 External Port Edge Trigger ADC       106         12.3.2 PWM Triggered ADC       106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10.4.4   | 4 T3 -Mode3 (Two separate 8-bit timers)           | 99  |

| 10.5.2 T4 - Mode1 (16 - bit Timing Mode)       .100         10.5.3 T4- Mode2 (8-bit automatic reload timing mode)       .101         10.5.4 T4- Mode3 (stop counting)       .101         1. BUZZER       .102         2. ANALOG TO DIGITAL CONVERSION (ADC)       .103         12.1 ADC Overview       .103         12.2 ADC Configuration       .104         12.2.1 Port Configuration       .104         12.2.2 Channel Selection       .104         12.2.3 ADC Reference Voltage       .104         12.2.4 Conversion Clock       .104         12.2.5 ADC Interrupt       .105         12.2.6 Result Formatting       .105         12.3 ADC Hardware Triggered Start       .106         12.3.1 External Port Edge Trigger ADC       .106         12.3.2 PWM Triggered ADC       .106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10.5     | Timer4 Operation Mode                             | 100 |

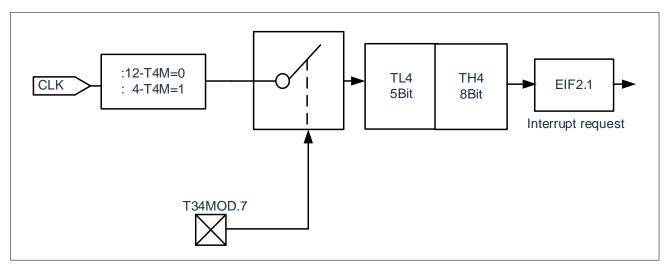

| 10.5.3 T4- Mode2 (8-bit automatic reload timing mode).       .101         10.5.4 T4- Mode3 (stop counting).       .101         1. BUZZER.       .102         2. ANALOG TO DIGITAL CONVERSION (ADC).       .103         12.1 ADC Overview.       .103         12.2 ADC Configuration.       .104         12.2.1 Port Configuration.       .104         12.2.2 Channel Selection.       .104         12.2.3 ADC Reference Voltage.       .104         12.2.4 Conversion Clock.       .104         12.2.5 ADC Interrupt.       .105         12.2.6 Result Formatting.       .105         12.3 ADC Hardware Triggered Start.       .106         12.3.1 External Port Edge Trigger ADC.       .106         12.3.2 PWM Triggered ADC.       .106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10.5.1   | 1 T4 -Mode0 (13 -bit timing mode)                 | 100 |

| 10.5.4 T4- Mode3 (stop counting)       101         1. BUZZER       102         2. ANALOG TO DIGITAL CONVERSION (ADC)       103         12.1 ADC Overview       103         12.2 ADC Configuration       104         12.2.1 Port Configuration       104         12.2.2 Channel Selection       104         12.2.3 ADC Reference Voltage       104         12.2.4 Conversion Clock       104         12.2.5 ADC Interrupt       105         12.2.6 Result Formatting       105         12.3 ADC Hardware Triggered Start       106         12.3.1 External Port Edge Trigger ADC       106         12.3.2 PWM Triggered ADC       106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10.5.2   | 2 T4 -Mode1 (16 -bit Timing Mode)                 | 100 |

| 1. BUZZER       102         2. ANALOG TO DIGITAL CONVERSION (ADC)       103         12.1 ADC Overview       103         12.2 ADC Configuration       104         12.2.1 Port Configuration       104         12.2.2 Channel Selection       104         12.2.3 ADC Reference Voltage       104         12.2.4 Conversion Clock       104         12.2.5 ADC Interrupt       105         12.2.6 Result Formatting       105         12.3 ADC Hardware Triggered Start       106         12.3.1 External Port Edge Trigger ADC       106         12.3.2 PWM Triggered ADC       106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | ,                                                 |     |

| 2. ANALOG TO DIGITAL CONVERSION (ADC)       103         12.1 ADC Overview       103         12.2 ADC Configuration       104         12.2.1 Port Configuration       104         12.2.2 Channel Selection       104         12.2.3 ADC Reference Voltage       104         12.2.4 Conversion Clock       104         12.2.5 ADC Interrupt       105         12.2.6 Result Formatting       105         12.3 ADC Hardware Triggered Start       106         12.3.1 External Port Edge Trigger ADC       106         12.3.2 PWM Triggered ADC       106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10.5.4   | 4 T4- Mode3 (stop counting)                       | 101 |

| 12.1 ADC Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11. BUZ  | ZER                                               | 102 |

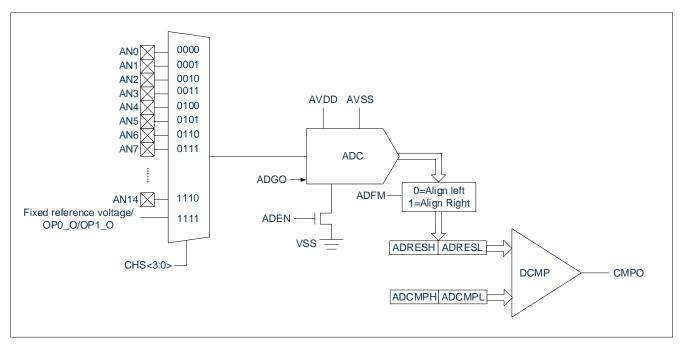

| 12.1 ADC Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12. ANA  | ALOG TO DIGITAL CONVERSION (ADC)                  | 103 |

| 12.2.1 Port Configuration       104         12.2.2 Channel Selection       104         12.2.3 ADC Reference Voltage       104         12.2.4 Conversion Clock       104         12.2.5 ADC Interrupt       105         12.2.6 Result Formatting       105         12.3 ADC Hardware Triggered Start       106         12.3.1 External Port Edge Trigger ADC       106         12.3.2 PWM Triggered ADC       106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | • • •                                             |     |

| 12.2.2 Channel Selection       104         12.2.3 ADC Reference Voltage       104         12.2.4 Conversion Clock       104         12.2.5 ADC Interrupt       105         12.2.6 Result Formatting       105         12.3 ADC Hardware Triggered Start       106         12.3.1 External Port Edge Trigger ADC       106         12.3.2 PWM Triggered ADC       106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12.2     | ADC Configuration                                 | 104 |

| 12.2.3 ADC Reference Voltage       104         12.2.4 Conversion Clock       104         12.2.5 ADC Interrupt       105         12.2.6 Result Formatting       105         12.3 ADC Hardware Triggered Start       106         12.3.1 External Port Edge Trigger ADC       106         12.3.2 PWM Triggered ADC       106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12.2.1   | Port Configuration                                | 104 |

| 12.2.4 Conversion Clock       104         12.2.5 ADC Interrupt       105         12.2.6 Result Formatting       105         12.3 ADC Hardware Triggered Start       106         12.3.1 External Port Edge Trigger ADC       106         12.3.2 PWM Triggered ADC       106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12.2.2   | 2 Channel Selection                               | 104 |

| 12.2.5 ADC Interrupt       105         12.2.6 Result Formatting       105         12.3 ADC Hardware Triggered Start       106         12.3.1 External Port Edge Trigger ADC       106         12.3.2 PWM Triggered ADC       106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12.2.3   | 3 ADC Reference Voltage                           | 104 |

| 12.2.6 Result Formatting       105         12.3 ADC Hardware Triggered Start       106         12.3.1 External Port Edge Trigger ADC       106         12.3.2 PWM Triggered ADC       106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12.2.4   | 4 Conversion Clock                                | 104 |

| 12.3 ADC Hardware Triggered Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12.2.5   | 5 ADC Interrupt                                   | 105 |

| 12.3.1 External Port Edge Trigger ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12.2.6   | 6 Result Formatting                               | 105 |

| 12.3.2 PWM Triggered ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12.3     | ADC Hardware Triggered Start                      | 106 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12.3.1   | 1 External Port Edge Trigger ADC                  | 106 |

| 12.3.3 Hardware trigger delay before starting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12.3.2   | 2 PWM Triggered ADC                               | 106 |

| 12.0.0 Traitural diliggor dolay soloro otaliang                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12.3.3   | 3 Hardware trigger delay before starting          | 106 |

| 12.4 ADC Operating Principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12.4     | ADC Operating Principle                           | 107 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12.4.1   | 1 Start Conversion                                | 107 |

| 12.4.1 Start Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12.4.2   | 2 Complete Conversion                             | 107 |

| 12.4.1 Start Conversion       107         12.4.2 Complete Conversion       107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12.4.3   | 3 Terminate Conversion                            | 107 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12.4.4   | 4 A/D Conversion Step                             | 108 |

| 12.4.2 Complete Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12.4.5   | 5 Conversion During Sleep Mode                    | 108 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12.4.1   | 1 Start Conversion                                | 107 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                                   |     |

| 12.4.2 Complete Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                                                   |     |

| 12.4.2 Complete Conversion   107     12.4.3 Terminate Conversion   107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                                                   |     |

| 12.4.2 Complete Conversion       107         12.4.3 Terminate Conversion       107         12.4.4 A/D Conversion Step       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12.4.5   | o Conversion During Sieep ivioae                  | 108 |

| 12.5                 | ADC Related Register                                                         | 109 |

|----------------------|------------------------------------------------------------------------------|-----|

| 12.6                 | ADC Results Comparison                                                       | 114 |

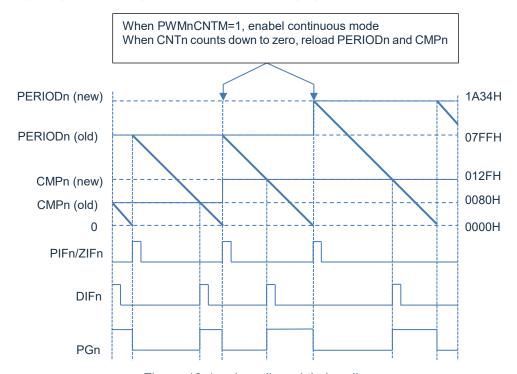

| 13. EN               | NHANCED PWM GENERATOR                                                        | 115 |

| 13.1                 | Overview                                                                     | 115 |

| 13.2                 | Features                                                                     | 115 |

| 13.3                 | Port Configuration                                                           | 116 |

| 13.4                 | Function description                                                         | 117 |

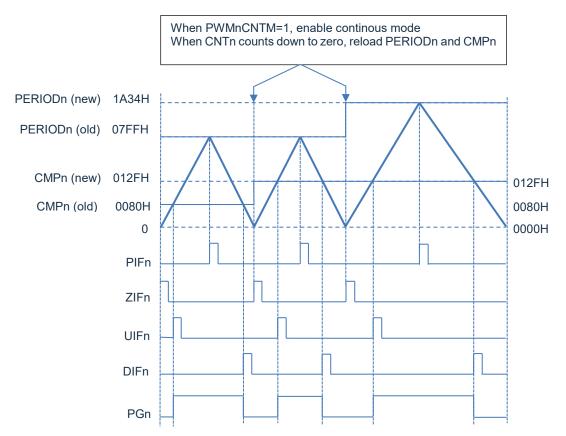

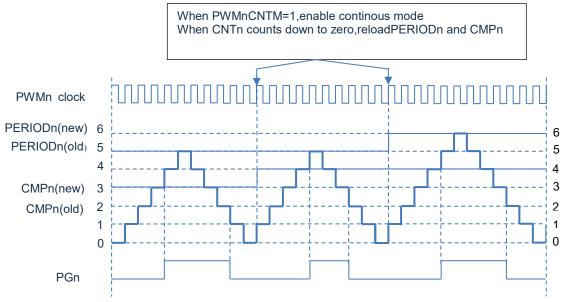

| 13.4                 | .4.1 Edge-aligned                                                            | 117 |

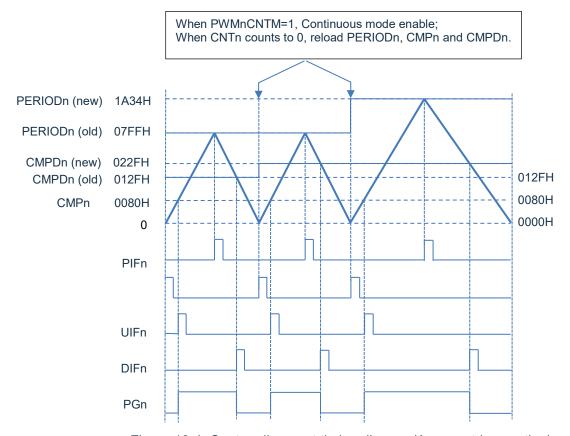

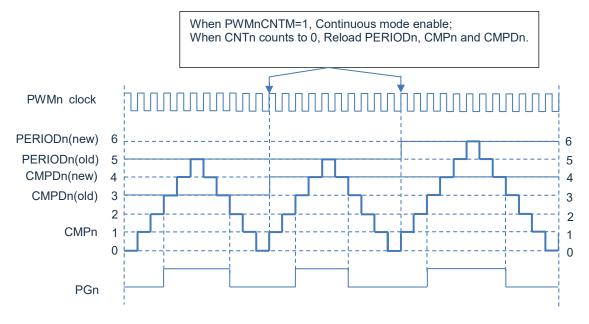

| 13.                  | 4.2 Center-aligned                                                           | 118 |

| 13.                  | 4.3 Complementary Mode And Dead Zone Delay                                   | 122 |

| 13.4                 | 4.4 Brake Function                                                           | 122 |

| 13.5                 | PWM Related Register                                                         | 123 |

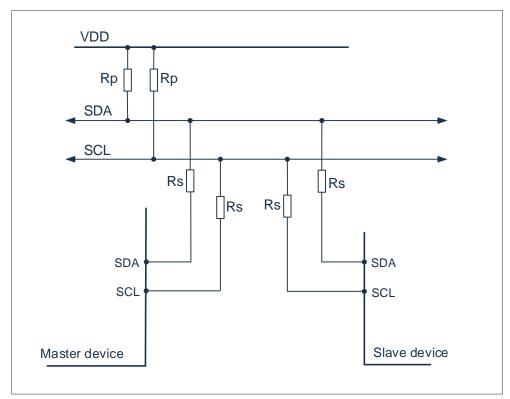

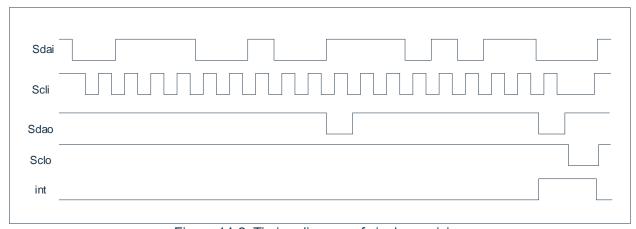

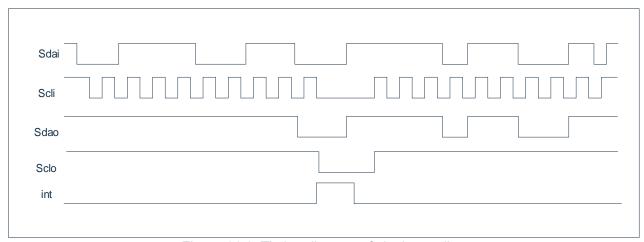

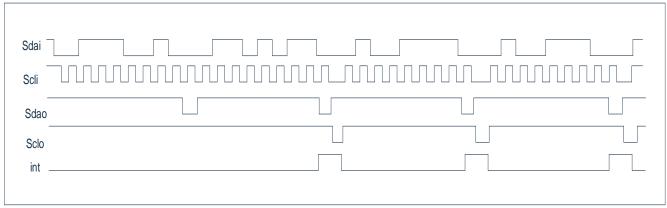

| 14. I <sup>2</sup> C | C MODULE                                                                     | 133 |

| 14.1                 | Overview                                                                     | 133 |